迎接可穿戴设备时代的设计挑战

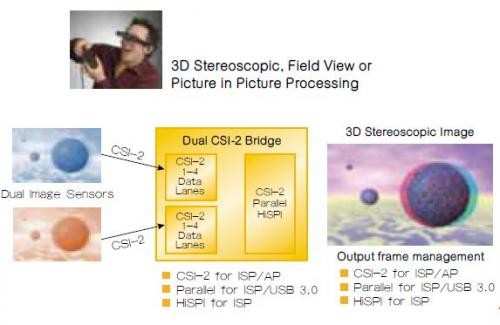

桥接功能也可用作基于FPGA的更大系统元件的构建模块,如实现图4中的双输入桥接/处理器,它将接收来自2个独立图像传感器的CSI-2串行数据流,并将其处理为单个CSI-2或并行或HiSPI输出。根据所选的算法,可对独立的数据流进行色彩调整或在时间或空间上进行补偿生成单幅3D图像,或在屏幕坐标空间的不同位置对其单独显示产生画中画效果。

图4:FPGA可用于实现实时视频处理功能,如生成3D立体图像、视场或画中画

FPGA助力节能技术

在前面的几个例子中,设计的主要目的是为了增强应用处理器本身的互连或功能。但这些基于FPGA的解决方案还提供了另一个重要的好处:使得MCU或ASSP无需同时执行一个或多个计算密集型任务,从而节省了有限的处理器资源。

但是,在许多情况下,这些设计的功耗降低具有更重要的意义。例如,图3中的设计包含了一个硬件屏幕刷新功能,其仅需消耗传统处理器内核所需功率的一小部分。同样,图4中的一些小尺寸、低功耗FPGA逻辑器件独立于主机处理器执行图像处理任务,这使得主机处理器大部分时间可处于节能睡眠模式。

下面探讨的许多应用都使用这种节能设计方法,适用于大多数有低功耗需求的可穿戴应用。

FPGA可加速设计升级和新设计实现

可穿戴电子设备发展迅速,每一代新产品都比上一代添加了更多的功能和特性。在这些应用中,小尺寸、低成本的FPGA经常被用来扩展可穿戴式设备应用处理器的基本功能。

许多现代的微控制器都有强大的计算能力来管理传感器和处理其产生的数据,并将它与其他数据流进行整合。但使用微控制器来完成这些工作会占用宝贵的I/O资源,并要求处理器长时间处于工作状态,从而会影响电池寿命。

而FPGA可以用来创建半自主的I/O模块,能够从多个传感器收集数据,并在没有处理器干预的情况下完成其他高级功能。“永远在线”的低功耗计步器采用3轴加速度计作为主要传感器,记录佩戴者的步数,计算所走的距离并测定燃烧的卡路里以及运动时间。

在该设计中,一些FPGA逻辑单元被配置用作加速度计的I2C接口和应用处理器SPI/O总线之间的桥接。其他的FPGA功能块用于配置和管理加速度计。可编程逻辑也可以用于处理原始的加速度计数据,针对带有噪声的数据流采用统计学滤波和步数检测算法。FPGA的另一部分功能是用来缓存得到的步数和加速度信息,直到主机处理器从低功耗睡眠状态唤醒并收集这些数据。采用可编程逻辑内核来执行这些计算密集型任务,可使应用处理器长时间处于睡眠模式,从而有助于减少计步器的功耗。通过FPGA实现这些功能也使设计人员能够在不影响计步器的性能和精度的情况下,使用更简单、更低功耗的微控制器。

FPGA提供可扩展的解决方案

采用FPGA的另一个优点是,FPGA厂商通常会提供一系列类似的器件,每个器件有不同的可编程逻辑和I/O组合。使用FPGA作为ASIC的补充或替代,设计工程师可以选择他们目前所需的逻辑门数量,开发大小合适的解决方案。

由于同一FPGA系列的器件共享参数、特性和开发资源,各种逻辑密度和I/O配置选择使得制造商可以采取“升级时再购买”的策略,为现有的设计添加新的功能,或重组现有的功能开发新的产品。由于同一系列器件共享通用的工具链和IP库,设计工程师可以迅速将升级和后续设计从设想变为产品推向市场。

总结

可穿戴设备的标准架构、功能集和专用芯片的缺失为本来就面临紧张成本、功耗和尺寸约束的移动消费电子设计带来了许多前所未有的挑战。本文介绍了FPGA能够通过一些简单的方法帮助设计工程师解决上述问题,例如:为现有微控制器、传感器、显示器等之间的接口桥接,为现有的微控制器和ASSP添加新的互连和功能,以及在某些情况下提供了一种替代ASIC或SoC的选择。

由于其灵活性、可扩展性和较低的解决方案成本,FPGA为许多类型的产品重新定义了传统的设计周期,为设计工程师提供了许多超越传统ASIC的优点。

最新活动更多

推荐专题

- 1 影石全景相机,谁是盈利最强企业?

- 2 “中国版”Ray-ban Meta AI眼镜价格最低不到100元,“凶残”的华强北们

- 3 「百镜大战」,三大产品形态之争

- 4 AI眼镜赛道分化;2025年中国市场总销量预计增长188.5%

- 5 VR眼镜销量下滑,AI眼镜月活暴增4倍,Meta公司眼镜业务冰火两重天

- 6 Apple Watch SE 3爆料来袭,一起瞧瞧有哪些新亮点!

- 7 苹果Vision Pro还能撑多久,库克或押宝智能眼镜,下一代产品最早年底亮相

- 8 阿里、字节终结百镜大战?

- 9 Ray-Ban Meta迎来全面升级,占六成市占率的Meta加速布局AI智能眼镜

- 10 暴跌45.8%!又一门隐秘生意扛不住了

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论